Do you need Wafer Lot Acceptance to Mil-Std-883, Method 2018? This post explores the purpose and importance of this standard when performing electronics failure analysis.

What is MIL-STD-883

MIL-STD-883 is US military test standard for testing microelectronic devices. The objective of MIL-STD-883 is to identify devices suitable for use within military and aerospace electronic systems that withstand the harmful effects of natural elements and conditions.

Wafer Lot Acceptance to Mil-Std-883, Method 2018

The Mil-Std- 883, Method 2018 specifies sampling procedures for die selected from the wafers or die already packaged. In this post, we dive into the purpose and processes required by this standard.

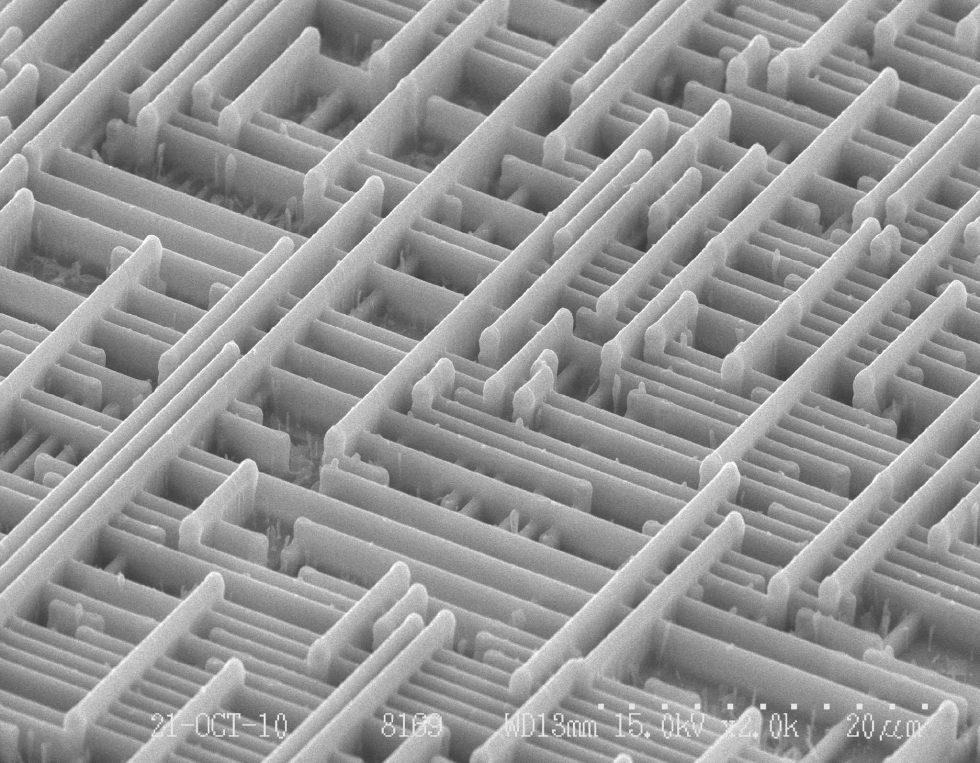

Scanning Electron Microscope (SEM) Inspections are defined in Mil-Std-883, Method 2018, and form part of a Wafer Lot Acceptance (WLA) plan. The purpose of this standard is to ensure metallization layers in the integrated circuit (IC) do not suffer from systemic processing problems.

Although WLA is not typically cited for industrial environments, the mission-critical components in the military and aerospace marketplaces for Method 2018 are commonplace as a requirement for integrated circuit wafers and die.

The Importance of Method 2018

One purpose of Method 2018 is to ensure a wafer processing lot has metal layers that are at least 50% of their designed cross-sectional area for current densities.

Metal layers processed on a planar technology are typically not a concern; however, in non-planarized processes, the oxide steps can result in thinning of the metal and therefore decrease the cross-sectional areas.

These metal step coverage concerns can result in failures if the cross-sectional areas are too thin for the designed current density criteria required by Mil-PRF-38535 and lead to localized current hot spots that could result in blown metal lines or long-term failures from electromigration.

Method 2018 is focused on characteristics of the metal layers that are evaluated across the wafer lot, and not random defects, such as scratches, smeared metal, etc.

Statistically, a very large sample size would be required to validate a particular wafer lot. The Mil-Std- 883, Method 2018 specifies sampling procedures for die selected from the wafers or die already packaged. A sampling of 8 dies is required if there is wafer lot traceability or 22 samples of a population of devices that do not have traceability back to the wafer lot.

The metal inspection can begin, once the samples have been selected. Typically samples are pulled from completed wafer lots, although Mil-Std- 883, Method 2018 does provide some guidelines for pulling samples before final glassivation.

Assuming the samples are from completed wafers, the top glassivation layer will need to be removed before the metal lines can be SEM inspected. The maximum SEM magnification required by Method 2018 is 50,000x, with an SEM resolution of 250 angstroms or less. For the SEM inspection, the use of a conductive coating on the specimen is discouraged. Thankfully, a good Field Emission SEM (FE-SEM) easily meets all these requirements.

The next layer of metallization will need to be uncovered and inspected after the top layer metallization has been inspected. The top metal and the glassivation layer beneath the top metallization must be removed to inspect the next layer of metallization. This selective deprocessing should not disturb the underlying metal layer to allow the inspection of the next metal layer.

This process is repeated for each metal layer, meticulously removing the top metal layer and oxide to get to the next metal layer without causing any damage. It is possible, using dry etch techniques, to expose multiple metal layers at a time; this is allowed under the regulations of Method 2018 and can increase the efficiency of the inspection process, saving time and money.

Another requirement of Mil-Std-883, Method 2018 is the performance of a cross-section of the sample, either by lapping or cleaving. This additional step is performed at areas of interest, based upon the top view examination already performed, to allow an accurate measurement of the metallization thickness on a planar region, the metallization thickness over the step coverage, and a view of any suspect structures or process artifacts (but still not random defects). Obviously, cross-sections in the x- and y-planes are the minimum needed, and on occasion, a customer may also provide areas of interest (based upon their knowledge of a specific structure that might be unique).

The SEM inspection itself is straightforward, but the deprocessing of each metal layer and oxide to the next metal requires a lab with considerable experience in this area of expertise. Most non-planar processes only have three levels of metal or less, however, the irregularities in the metal heights (mountains and valleys if you will) can be considerable.

To perform a proper inspection, it may be necessary to etch the glassivation layer in the valley to expose the metal therein, while leaving the metal atop the “mountain” intact. Although the latest version of Method 2018 does not require inspection of planarized processes, there are some IC users who still require this inspection. In these cases, there can be upwards of 8 layers of metal to be inspected and subsequently removed.

Furthermore, the mainstream wafer processes are now including some or all copper metallization in IC manufacturing. The process of removing copper metallization is much different than that of aluminum, and if there is a subsequent layer of aluminum under the copper layer, the deprocessing also needs to take that under consideration.

Any misprocessing when removing the metal and glass layer will be compounded by the ensuing deprocessing steps, potentially rendering the sample useless for the examination of the lower metallization levels. Method 2018 foresaw such issues and allows the sampling of a second die (adjacent to the first one sampled) as a replacement).

It is still necessary, though, to deprocess the top levels of metal to resume the inspection of the lower levels. This can be a very costly process if too many mistakes are made, or for some labs, not even feasible. Obviously, each time a sample has to be started over, there will be a delay in the time to finishing the inspection and hence a delay in releasing the wafer lot for production.

While no electronic failure analysis lab will deprocess every die perfectly, it is obviously desirable to select a lab with a successful track record, one that will minimize costs and time delays. As such, the selection of the lab to perform the SEM inspection should focus on reputable labs with the experience, knowledge, and capability to meet your needs.

Mil-Std-883, Method 2018 specifies the requirements for the SEM Inspection of metallization layers of integrated circuits. It is a very complete document detailing how to prepare for and inspect the metallization layers in order to accept a wafer lot. One of the key ingredients is working with a failure analysis laboratory that you know has the appropriate equipment, technical know-how, and experience in deprocessing and inspecting to this standard.