Wafer Test & Sort

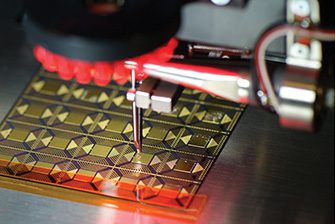

Probe Testing

Wafer-level probe testing applies a programmed test pattern to each die on the wafer to collect data about the electrical circuit. Spirit offers a vast array of electrical tests to meet application-specific data needs depending on the wafer complexity. Our process is cost-effective based on die size, number of touch downs and performance to maximize the rate of return and optimize test coverage to the data sheet.

Sort & Bin

Wafer probe testing determines the reliability and performance limits of each die on the wafer. This data allows you to sort die into performance ranges, optimizing each die’s performance in application. This is especially useful for die stacking and multi-chip designs. Binning reduces low-lot yields, production cost and rework.

Three Temp Test

Electrical testing at three temperatures covers additional test parameters for quality and integrity of the die in harsh-environment or mission-critical applications.

Wafer Test Capabilities

- Wafer Speed Binning

- Wafer Temperature Binning

- Wafer “in family” data segregation

- Known Good Die

- Waffle/Gel Pack sorting

- Function Tests

- AC parameters

- DC parameters

- Application specific I/O test

- Customer configured testing

- Data sheet verification

- Anti-counterfeit validation

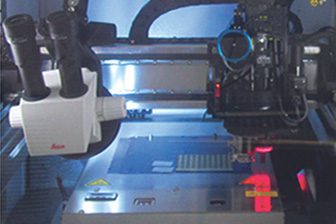

Wire Bonding

Wire bonding is a key manufacturing process for microelectronics and MEMS sensor products. The core wire bonding capabilities and expertise at Spirit Electronics support process development, testing, and manufacturing of sub-assemblies designed by our customers. Wire bonding processes are flexible and robust, allowing our customers to quickly realize a microelectronic package assembly solution for their products. For additional information you can contact us to discuss your wire bonding needs.

FINE GAUGE WIRE / RIBBON BONDING SPECIFICATIONS

- Wire diameters: 17.5µm to 50µm (0.7 to 2.0 mil)

- Ribbon: 6×35µm to 25×250µm (0.25×1.4 mil to 1×10 mil)

- Wire and ribbon materials: aluminum, gold

- Fine pitch is available

- Bond area: 305mm x 410mm (12.3” x 16.14”)

- Accuracy: 1um at 3 sigma

- Speed: up to 6 wires/second

- Loop Length: 70 µm up to 20 mm, depending on wire diameter

- Various loop form functions:

• Constant wire length

• Constant loop height

• Individual loop shapes

GOLD BALL BONDING SPECIFICATIONS

- Wire diameters: 15 to 50µm (0.6 to 2.0 mil)

- Wire materials: gold

- Fine pitch capability: 40µm

- Minimum loop height: 100µm (standard and worked loops)

- Bond area: 56mm x 80mm

- Accuracy: +/- 2.0µm

- Speed: up to 15 bonds/second including programmable looping

- Looping capability: standard and worked (BGA1-BGA3, Spider, J Wire, CSB)

- Stand-off Stitch bond (SSB) capable

- Stud bumping

- Wire material: gold

- Speed: Up to 30 bumps/second including programmable smoothing

HEAVY GAUGE WIRE / RIBBON BONDING SPECIFICATIONS

- Wire diameters: 100µm to 500µm (4 to 20 mil)

- Ribbon: 0.075×0.75mm to 0.4mm x 2mm (3×30 mil to 16×80 mil)

- Wire and ribbon materials: aluminum

- Bond area: 300mm x 500mm (13.8” x 19.7”)

- Accuracy: 2µm at 3 sigma

- Speed: up to 3 wires/sec

Failure Protection

Products testing outside of specifications or standards pose a failure risk. Improperly leaded finishes can result in whiskering over time.

If your product fails analysis, you can take immediate action to refinish leads, or in the case of failed connection mapping, disqualify an entire lot. Ask us about our testing warranty protection to prevent failures from impacting cost and production time.